Deepak Kumar Tala 6 ----- 7 module rom_using_file 8 address Address input 9 data Data output 10 read_en Read Enable 11 ce Chip Enable 12. Public anyone with the link can view Published will appear in search results Private only you can view Save.

Ram And Rom Verilog Pdf Electronic Engineering Electronic Design

Other tools which use Verilog such as synthesis will make their own interpretation of the Verilog language.

. Teach Yourself Verilog With This Tiny CPU Design. Verilog RAM RTL code. Implement synchronous RAM Random Access Memory and also provide a test-bench to validate it.

End Or reg 40 ROM 630. As follows refer to Verilog slicing link for further information. Provides broad coverage of Verilog HDL topics - from basic.

Rom_using_filev 4 Function. Each section shows the list of Verilog-files require to implement the design in that section. RAM Verilog Code ROM Verilog Code.

33270 views and 19 likes. I created a simple ROM module in Verilog 2 bit address addr and 8 bit data output data I have also created a block design microblaze project with a uart that I have been able to send things out of in the past. Designing Rom In Verilog.

Synthesis tools are able to detect single-port RAM designs in the HDL code and automatically infer either the altsyncram or the altdpram megafunctions depending on the architecture of the target device. Coefficient Multiplier always posedge clk c RAM - flow through if c_ram_en if c_ram_wr begin c_RAMi. Introduction to Verilog Chip Design Flow Chip Abstraction Layers Data Types Verilog Syntax Verilog Data types Verilog ScalarVector Verilog Arrays Building Blocks.

Designing a ROM block ie a sequential circuit that can perform different mathematical function. - GitHub - anupkumar-siucROM-Memory-Design-Using-Verilog. RF and Wireless tutorials.

Childrens World Atlas With CDROM 9780756675844 0756675847. The FIFO width is chosen to compensate for the Transfer rate and is calculated as. So prefer using mixed block array.

Y is necessarily a constant. There is no difference or perhaps a little difference between using packed and unpacked arrays. All youll want to do will be to introduce some glitter in.

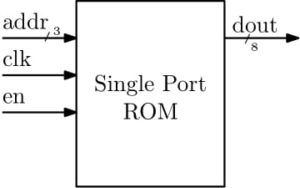

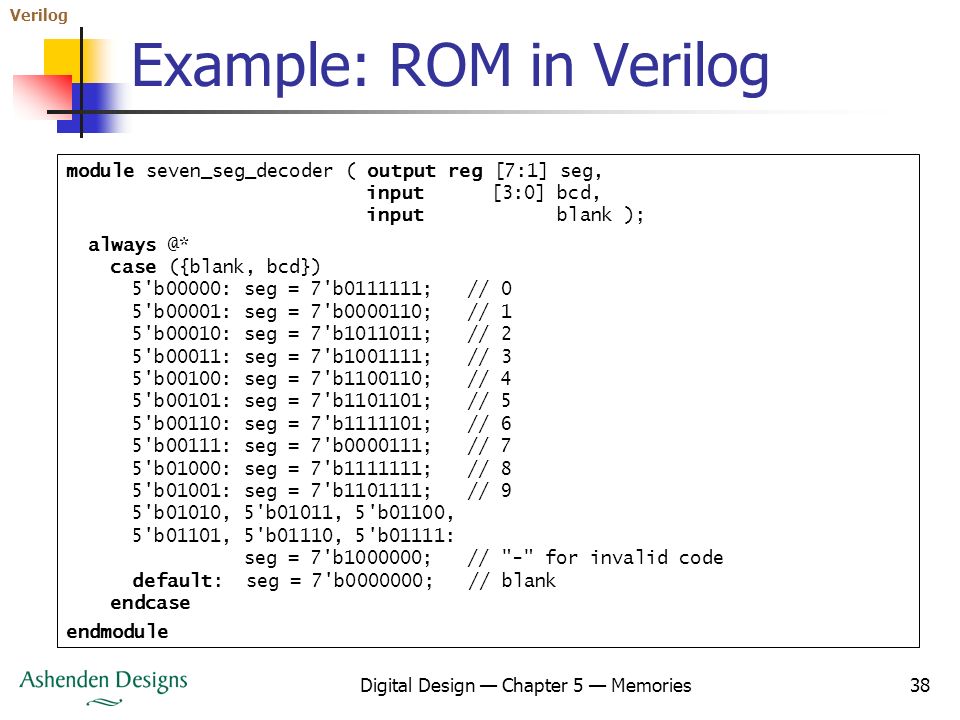

The Quartus II software and Verilog HDL support several library of parameterized modules LPM functions and other megafunctions that allow you to implement RAM and ROM in Altera devices. Following is the figure and verilog code of RAM Random Access Memory. Verilog Digital Design Chapter 5 Memories 16 Example.

For Verilog HDL digital IC and system design professionals. 13 input 70 address. Which can be used to implement the design using some other software as well.

Random Access Memory example. It can be constructed from 32 full adder cells each of which in turn requires about six 2-input gates. Download Designing Video Game Hardware In Verilog PDFePub or read online books in Mobi eBooks.

With schematics a 32-bit adder is a complex design. Reg 40 ROM 630. Set the desired design as top-level.

1 ----- 2 Design Name. The Transfer rate may differ due to difference in number of ports frequency or data-width between source and destination. Designing Video Game Hardware In Verilog.

A Guide to Digital Design and Synthesis With CDROM Hardcover ed 0130449113 9780130449115. The definition of Verilog for simulation is cast in stone and enshrined in the Language Reference Manual. Click Download or Read Online button to get Designing Video Game Hardware In Verilog book now.

Fifo first-in-first-out are used to for serial transfer of information whenever there is a difference of Transfer rate. About Press Copyright Contact us Creators Advertise Developers Terms Privacy Policy Safety How YouTube works Test new features Press Copyright Contact us Creators. All the design files are provided inside the VerilogCodes folder inside the main project directory.

17 18 reg 70 mem 0255. You probably couldnt write a decent novel if youd never read a novel. Home Interview Basics Design RTL VLSI Python LTE.

234 6 40MB Read more. Always posedge clk y register if y_ce begin if mult_sel begin operand1 c_out. Designing a ROM block ie a sequential circuit that can perform different mathematical function.

Rom_using_file 3 File Name. Y the start position is x and count down from x by Y. Lastly all designs are tested using Modelsim and on Altera-DE2 FPGA board.

This example describes a 64-bit x 8-bit single-port RAM design with common read and write addresses in Verilog HDL. Learning to do something often involves studying what other people did. Random Access Memory example.

ROM in verilog If you use ROM for emulation you can use this construct for example. 14 output 70 data. Alwaysnegedge reset ifreset begin ROM0.

This complete Verilog HDL reference progresses from the basic Verilog concepts to the most advanced concepts in digital design. Verilog provides a much more compact description. Design module single_port_sync_ram parameter ADDR_WIDTH 4 parameter DATA_WIDTH 32 parameter DEPTH 16 input clk.

The generic scalable nature of each of these functions ensures that you can use them to implement any supported type of RAM or ROM. End But you should use Macro from FAB if youre going to synthesize real ASIC. Synchronous Random Access Memory RAM implementation in Verilog.

For loading data into ROM from a file refer to this link. End else c_out. Verilog HDL is a language for digital design just as C is a language for programming.

Comparison between RAM and ROM. This site is like a library Use search box in the widget to get ebook that you want. Module addera b y.

13641-2002 but no vendor adheres strictly to it. There is an IEEE standard for Verilog synthesis IEEE Std. Designing rom in verilog It is easier than straightforward to develop exceptional nail artwork for short nails.

Synchronous FIFO. ROM using readmemh 5 Coder. This revised edition of DKs groundbreaking 2003 atlas has been refreshed with beautiful bright new maps a topic.

Memory Design Digital System Design

Ram Verilog Code Rom Verilog Code Ram Vs Rom

Design Of Rom In Verilog Youtube

Logikai Tervezes Hardverleiro Nyelven Ppt Video Online Download

Digital Design An Embedded Systems Approach Using Verilog Ppt Video Online Download

0 comments

Post a Comment